# INTRINSIC NOISE CURRENTS IN DEEP SUBMICRON MOSFETS

Chih-Hung Chen<sup>1</sup>, M. Jamal Deen<sup>1</sup>, Yuhua Cheng<sup>2</sup> and Mishel Matloubian<sup>2</sup>

<sup>1</sup>Electrical and Computer Engineering, McMaster University, Hamilton, ON, Canada

<sup>2</sup>Conexant Systems Inc., Newport Beach, California, U.S.A.

## ABSTRACT

A systemic extraction method to obtain the induced gate noise ( $i_g i_g^*$ ), channel thermal noise ( $i_d i_d^*$ ) and their cross-correlation term ( $i_g i_d^*$ ) in sub-micron MOSFETs directly from scattering and RF noise measurements is presented and verified with measurements. The extracted noise currents versus frequency, bias condition and channel length for MOSFETs from a  $0.18\mu\text{m}$  CMOS process are presented and discussed.

## INTRODUCTION

Currently, there is a trend to replace RFICs with BJTs and GaAs FETs with deep submicron MOSFETs which have unity current-gain frequencies ( $f_T$ ) of several tens of GHz [1]. However, for many RFICs, low noise performance is very important. Therefore, RF noise modeling of deep submicron MOSFETs is very important for devices used in the front-end transceivers. Because of the difficulties in the extraction of the induced gate noise and its correlation term with the channel thermal noise, several noise models [2],[3] and simulation results [4] have been presented, but they could not be verified directly with RF noise measurements for deep submicron MOSFETs. In this paper, a systematic procedure to extract the induced gate noise, channel thermal noise and their cross-correlation directly from the scattering and RF noise measurements is presented. The extracted noise currents of the MOSFETs fabricated in a  $0.18\mu\text{m}$  CMOS process versus frequency, bias condition and channel length are presented and discussed.

## NOISE SOURCE EXTRACTION

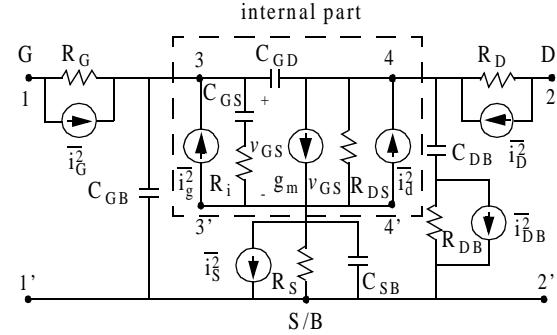

Fig. 1 shows the noise equivalent circuit model of an intrinsic MOSFET that is suitable for RF applications. It consists of two parts - an internal part which consists of  $C_{GS}$ ,  $C_{GD}$ ,  $R_i$ ,  $g_m$ ,  $R_{DS}$ ,  $i_g i_g^*$  (or  $i_g^2$ ) and  $i_d i_d^*$  (or  $i_d^2$ ), and an external part which includes all

the components outside of the dashed box, such as  $R_G$ ,  $C_{GB}$ ,  $R_S$ ,  $R_{SB}$ ,  $R_{DB}$ ,  $C_{DB}$  and  $R_D$ .

Fig. 1. The RF noise model of an intrinsic MOSFET that is suitable for high-frequency circuit applications.

After the devices and dummy structures, as described in [6], are fabricated, the induced gate noise, channel thermal noise and their correlation in MOSFETs can be extracted by using the following 15-step procedure [7].

1. Measure the scattering parameters  $S_{DUT}$ ,  $S_{OPEN}$ ,  $S_{THRU1}$  and  $S_{THRU2}$  of the device-under-test (DUT), OPEN, THRU1 and THRU2 dummy structures, respectively [6].

2. Measure the noise parameters (i.e.  $NF_{min,DUT}$ ,  $Y_{opt,DUT}$  and  $R_{n,DUT}$ ) of the device-under-test (DUT).

3. Perform the parameter de-embedding to obtain the intrinsic scattering ( $Y_{dev}$ ) and noise parameters ( $NF_{min,dev}$ ,  $Y_{opt,dev}$  and  $R_{n,dev}$ ) of the transistor [6].

4. Perform the parameter extraction based on  $Y_{dev}$  and other measured data to obtain all the element values (e.g.  $g_m$ ,  $C_{GS}$ ,  $C_{GD}$ , etc.) in the RF noise equivalent circuit model [8].

5. Calculate the correlation matrix  $C_{Adev}$  of the intrinsic transistor as defined in [9],[10].

6. Calculate the four-port admittance matrix  $Y_{extr}$  of the external part as defined in Fig. 1 by excluding all noise sources,  $C_{gs}$ ,  $C_{gd}$ ,  $g_m$ ,  $R_{DS}$  and  $R_i$ , and partition  $Y_{extr}$  as

$$\mathbf{Y}_{extr} = \begin{bmatrix} \mathbf{Y}_{ee} & \mathbf{Y}_{ei} \\ \mathbf{Y}_{ie} & \mathbf{Y}_{ii} \end{bmatrix} \quad (2)$$

where  $\mathbf{Y}_{ee}$ ,  $\mathbf{Y}_{ei}$ ,  $\mathbf{Y}_{ie}$  and  $\mathbf{Y}_{ii}$  are  $2 \times 2$  matrixes.

7. Calculate the two-port admittance  $\mathbf{Y}_{intr}$  of the internal part shown in the RF transistor model.

8. Calculate the matrix  $\mathbf{D}$  as follows [10]

$$\mathbf{D} = -\mathbf{Y}_{ei}(\mathbf{Y}_{ii} + \mathbf{Y}_{intr})^{-1}. \quad (3)$$

9. Convert the noise correlation matrix  $\mathbf{C}_{Adev}$  to  $\mathbf{C}_{Ydev}$  by

$$\mathbf{C}_{Ydev} = \mathbf{T}_Y \mathbf{C}_{Adev} \mathbf{T}_Y^\dagger \quad (4)$$

where the  $\dagger$  in  $\mathbf{T}_Y^\dagger$  denotes Hermitian conjugation and the transformation matrix  $\mathbf{T}_Y$  is given by

$$\mathbf{T}_Y = \begin{bmatrix} -Y_{11,dev} & 1 \\ -Y_{21,dev} & 0 \end{bmatrix}. \quad (5)$$

10. Calculate the admittance noise correlation matrix  $\mathbf{C}_{Yextr}$  of the external part by [11]

$$\mathbf{C}_{Yextr} = 2kT\Re(\mathbf{Y}_{extr}) \quad (6)$$

where  $\Re(\cdot)$  denotes for the real part of the matrix elements, and partition  $\mathbf{C}_{Yextr}$  as

$$\mathbf{C}_{Yextr} = \begin{bmatrix} \mathbf{C}_{ee} & \mathbf{C}_{ei} \\ \mathbf{C}_{ie} & \mathbf{C}_{ii} \end{bmatrix} \quad (7)$$

where  $\mathbf{C}_{ee}$ ,  $\mathbf{C}_{ei}$ ,  $\mathbf{C}_{ie}$  and  $\mathbf{C}_{ii}$  are  $2 \times 2$  matrixes.

11. Calculate the admittance correlation matrix  $\mathbf{C}_{Yintr}$  of the internal part in Fig. 1 by

$$\mathbf{C}_{Yintr} = \mathbf{D}_i(\mathbf{C}_{Ydev} - \mathbf{C}_{ee})\mathbf{D}_i^\dagger - \mathbf{C}_{ie}\mathbf{D}_i^\dagger - \mathbf{D}_i\mathbf{C}_{ei} - \mathbf{C}_{ii} \quad (8)$$

where  $\mathbf{D}_i = \mathbf{D}^{-1}$ .

12. Convert  $\mathbf{Y}_{intr}$  to its chain representation  $\mathbf{A}_{intr}$

13. Convert  $\mathbf{C}_{Yintr}$  to its chain matrix form  $\mathbf{C}_{Aintr}$  by using

$$\mathbf{C}_{Aintr} = \mathbf{T}_A \mathbf{C}_{Yintr} \mathbf{T}_A^\dagger, \quad (9)$$

where  $\mathbf{T}_A$  is given by

$$\mathbf{T}_A = \begin{bmatrix} 0 & \mathbf{A}_{12, intr} \\ 1 & \mathbf{A}_{22, intr} \end{bmatrix}. \quad (10)$$

14. Calculate the noise parameters,  $NF_{min}$ ,  $Y_{opt}$  and  $R_n$  of the internal part in Fig. 1 from the noise correlation matrix  $\mathbf{C}_{Aintr}$  by the equations (29a) - (29c) in [10].

15. Calculate the power spectral density of the channel thermal noise  $i_d^2$  (or  $i_d i_d^*$ ), induced gate noise  $i_g^2$  (or  $i_g i_g^*$ ) and their cross-correlation term  $i_g i_d^*$  by

$$\frac{|i_d|^2}{\Delta f} = 4kT R_n |Y_{21,intr}|^2, \quad (11)$$

$$\frac{|i_g|^2}{\Delta f} = 4kT R_n \left\{ |Y_{opt}|^2 - |Y_{11,intr}|^2 + 2\Re[(Y_{11,intr} - Y_{cor})Y_{11,intr}^*] \right\} \quad (12)$$

$$\frac{|i_g i_d^*|}{\Delta f} = 4kT(Y_{11,intr} - Y_{cor})R_n Y_{21,intr}^* \quad (13)$$

where  $Y_{cor}$  is given by

$$Y_{cor} = \frac{NF_{min} - 1}{2R_n} - Y_{opt}. \quad (14)$$

## MEASUREMENT AND DISCUSSION

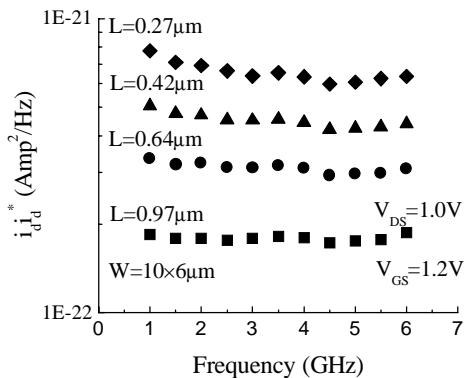

The DUTs are n-type MOSFETs fabricated in a  $0.18\mu\text{m}$  CMOS process by Conexant Systems Inc. Measurements were conducted by using an ATN NP5B Noise and S-parameter Measurement Systems (0.3 ~ 6 GHz). All the parasitic effects from probe pads and interconnections were de-embedded. Fig. 2 shows the channel thermal noise versus frequency characteristics for the n-type MOSFETs with channel width  $W = 10 \times 6\mu\text{m}$  (10 fingers) and lengths  $L = 0.97\mu\text{m}$ ,  $0.64\mu\text{m}$ ,  $0.42\mu\text{m}$  and  $0.27\mu\text{m}$ , respectively, biased at  $V_{DS} = 1.0\text{ V}$  and  $V_{GS} = 1.2\text{ V}$ .

Fig. 2. Extracted channel thermal noise ( $i_d i_d^*$ ) versus frequencies for devices of four different channel lengths.

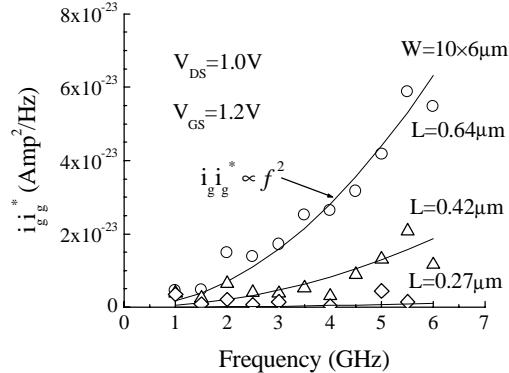

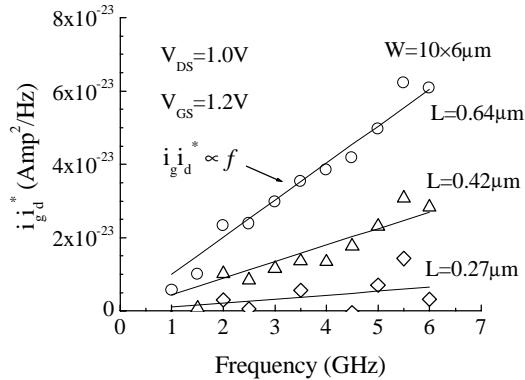

It is shown that the channel thermal noise, in general, is frequency independent and increases when the channel length decreases. From Figs. 3 and 4, the induced gate noise and the correlation term are proportional to  $f^2$  and  $f$  (solid lines), respectively, where  $f$  is the operating frequency. In addition, when channel length decreases, both the induced gate noise and the correlation term also decrease.

Fig. 3. Extracted induced gate noise ( $i_g i_g^*$ ) versus frequencies for devices of three different channel lengths.

Fig. 4. Extracted cross-correlation term ( $i_g i_d^*$ ) between the induced gate noise and the channel thermal noise versus frequencies for devices of three different channel lengths.

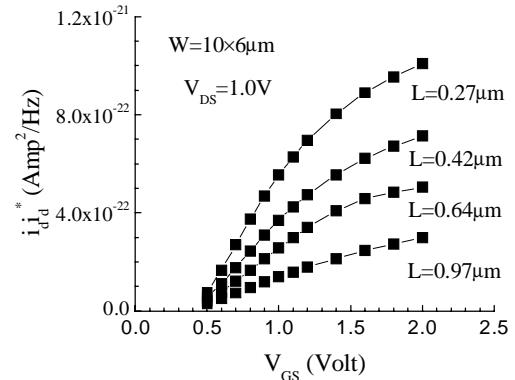

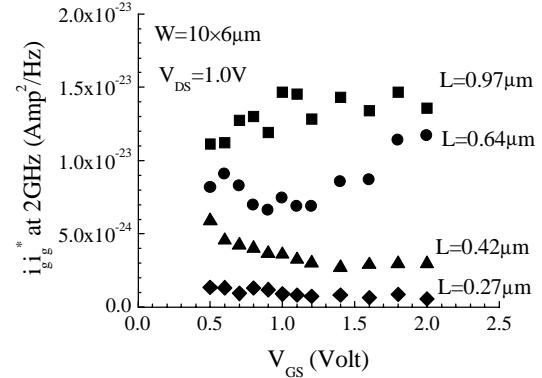

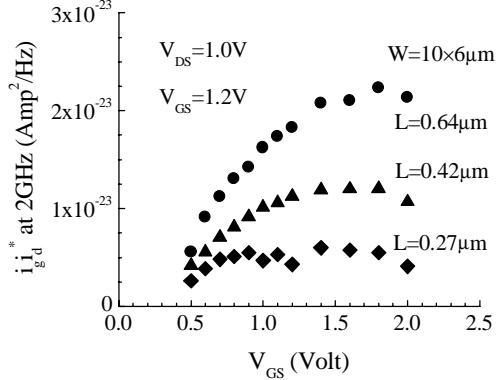

For the bias dependence of the extracted noise currents, Figs. 5, 6 and 7 show the  $i_d i_d^*$ ,  $i_g i_g^*$ , and  $i_g i_d^*$  versus  $V_{GS}$  characteristics for the n-type MOSFETs with channel width  $W = 10 \times 6\mu\text{m}$  and lengths  $L = 0.97\mu\text{m}$ ,  $0.64\mu\text{m}$ ,  $0.42\mu\text{m}$  and  $0.27\mu\text{m}$ , respectively, biased at  $V_{DS} = 1.0$  V. It is shown in Figs. 5 and 7 that  $i_d i_d^*$  and  $i_g i_d^*$  have a strong bias dependence and they increase when  $V_{GS}$  increases then tend to saturate at higher  $V_{GS}$  region. From Fig. 6, when  $V_{GS}$  increases,  $i_g i_g^*$  increases for longer channel

devices, but tends to decrease when the channel lengths decrease. It can be explained by the noise model proposed in [3]. For longer channel devices, the induced gate noise is dominant by the one generated in the channel region where the gradual channel approximation holds. The noise from this region tends to increase when  $V_{GS}$  increases. However, when the channel lengths decrease, the gate noise generated from the velocity saturation region becomes dominant and it tends to decrease when  $V_{GS}$  increases.

Fig. 5. Extracted channel thermal noise ( $i_d i_d^*$ ) versus  $V_{GS}$  characteristics for devices of four different channel lengths.

Fig. 6. Extracted induced gate noise ( $i_g i_g^*$ ) versus  $V_{GS}$  characteristics for devices of four different channel lengths.

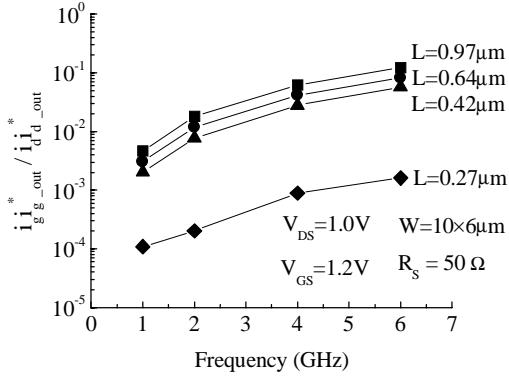

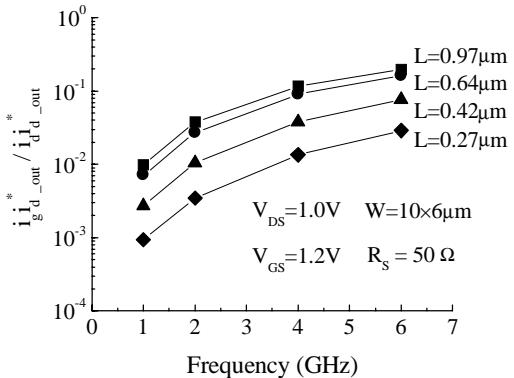

Finally, Figs. 8 and 9 show the ratio of the short-circuited output noise currents generated by  $i_g i_g^*$  and  $i_g i_d^*$  to that generated by  $i_d i_d^*$  with  $50\Omega$  source impedance when transistors were biased at  $V_{DS}=1.0$  V and  $V_{GS} = 1.2$  V. It is shown that  $i_g i_d^*$  contributes more noise currents than  $i_g i_g^*$  does at the

output port and both of them contribute less than 5% of the output noise current generated by  $i_d i_d^*$ .

Fig. 7. Extracted cross-correlation term ( $i_g i_d^*$ ) between the induced gate noise and the channel thermal noise versus  $V_{GS}$  characteristics for devices of three different channel lengths.

Fig. 8. The ratio of the output noise current from the induced gate noise ( $i_g i_g^*_{out}$ ) to the output noise from the channel thermal noise ( $i_d i_d^*_{out}$ ) as a function of frequencies with  $R_s = 50 \Omega$ .

Fig. 9. The ratio of the output noise current from the cross-correlation noise ( $i_g i_d^*_{out}$ ) to the output noise from the channel thermal noise ( $i_d i_d^*_{out}$ ) as a function of frequencies with  $R_s = 50 \Omega$ .

## CONCLUSION

The intrinsic noise sources in MOSFETs extracted from on-wafer scattering and noise measurements have been presented. From the extracted results of all tested devices, the channel thermal noise  $i_d i_d^*$  is frequency independent, increases when the channel length decreases for all bias conditions at a fixed  $V_{DS}$ , and is the most dominant noise source at the frequencies and bias conditions discussed. On the other hand,  $i_g i_g^*$  and  $i_g i_d^*$  have small noise contribution at the output port of transistors and less impact for the shorter channel devices. Therefore, an accurate and physics-based noise model for the channel thermal noise is crucial for MOSFETs when modeling RF low noise circuits.

## ACKNOWLEDGEMENT

This work was supported by Conexant Systems Inc. for device fabrication, and in part by grants from Conexant Systems Inc., Micronet, a federal network center of excellence in microelectronics, and the Natural Sciences and Engineering Research Council (NSERC) of Canada.

## REFERENCES

- [1] H. Samavati, H. R. Rategh and T. H. Lee, Solid-State Circuits, *IEEE Journal of Solid-State Circuits*, vol. 35 Issue 5 pp. 765 - 772, May 2000.

- [2] A. van der Ziel, *Solid state physical electronics*, 3rd ed., Prentice-Hall, Englewood Cliffs, NJ, 1976.

- [3] D. P. Triantis, A. N. Birbas and S. E. Plevridis, *Solid-State Electronics*, vol. 41, no. 12, pp. 1937-1942, 1997.

- [4] H. Nah, M. S. Chae, H. S. Min and Y. J. Park, *Proceedings of 1999 International Semiconductor Device Research Symposium*, pp. 215-218, 1999.

- [5] C. H. Chen and M. J. Deen, *Solid-State Electronics*, vol. 42(11), pp. 2069-2081, November 1998.

- [6] C. H. Chen and M. J. Deen, *IEEE Trans. on Microwave Theory and Techniques*, In Press (2001).

- [7] C. H. Chen and M. J. Deen, accepted in Proceedings of IEEE International Conference on Microelectronic Test Structures (ICMTS 2001), Japan 2001.

- [8] Christian C. Enz and Yuhua Cheng, *IEEE Journal of Solid-State Circuits*, vol. 35, no. 2, pp. 186-201, 2000.

- [9] H. Hillbrand and P. Russer, *IEEE Trans. on Circuits and Systems*, vol. CAS-23, no. 4, April 1976.

- [10] Robert A. Pucel, W. Struble, R. Hallgren and U. L. Rohde, *IEEE Trans. on MTT*, vol. 40, no. 11, pp. 2013 - 2024, 1992.

- [11] R. Q. Twiss, *Journal of Applied Physics*, vol. 26, pp. 599-602, May 1955.